Tektronix

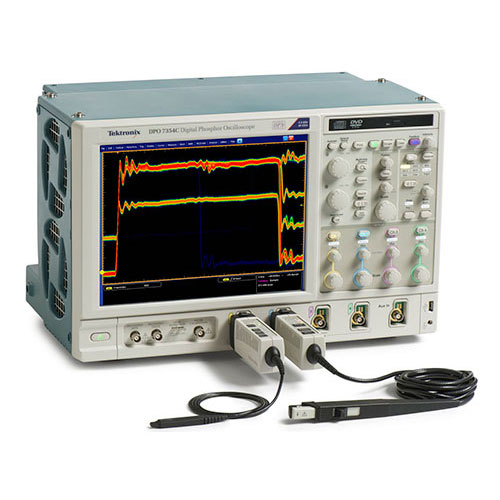

Tektronix builds test and measurement tools that meet high standards for quality. Transcat provides Tektronix spectrum analyzers, vector network analyzers, oscilloscopes, and probes, so our customers in manufacturing and testing environments can overcome rf and electronic measurement challenges. Our selection of Tektronix oscilloscopes covers the mixed domain, mixed signal, digital storage, digital phosphor, and handheld product categories. You can find a bench or portable oscilloscope in the specifications you need for design and compliance testing. We also stock a wide range of Tektronix probes that work seamlessly with the manufacturer’s oscilloscopes. Need Tek equipment quickly? Transcat stocks a wide inventory ready for immediate delivery and offers rental services for short or long-term projects. Order your Tektronix products with Transcat’s ISO 17025 accredited rf calibration services to ensure your equipment arrives ready to go.